Key Takeaways

- Increased transistor density and shifts in chip architecture are complicating traditional testing methods.

- Defects are emerging in clock trees and scan cell blocks, which can number in the millions.

- Machine learning is being utilized to optimize defect identification and testing processes.

Complexity in Chip Testing

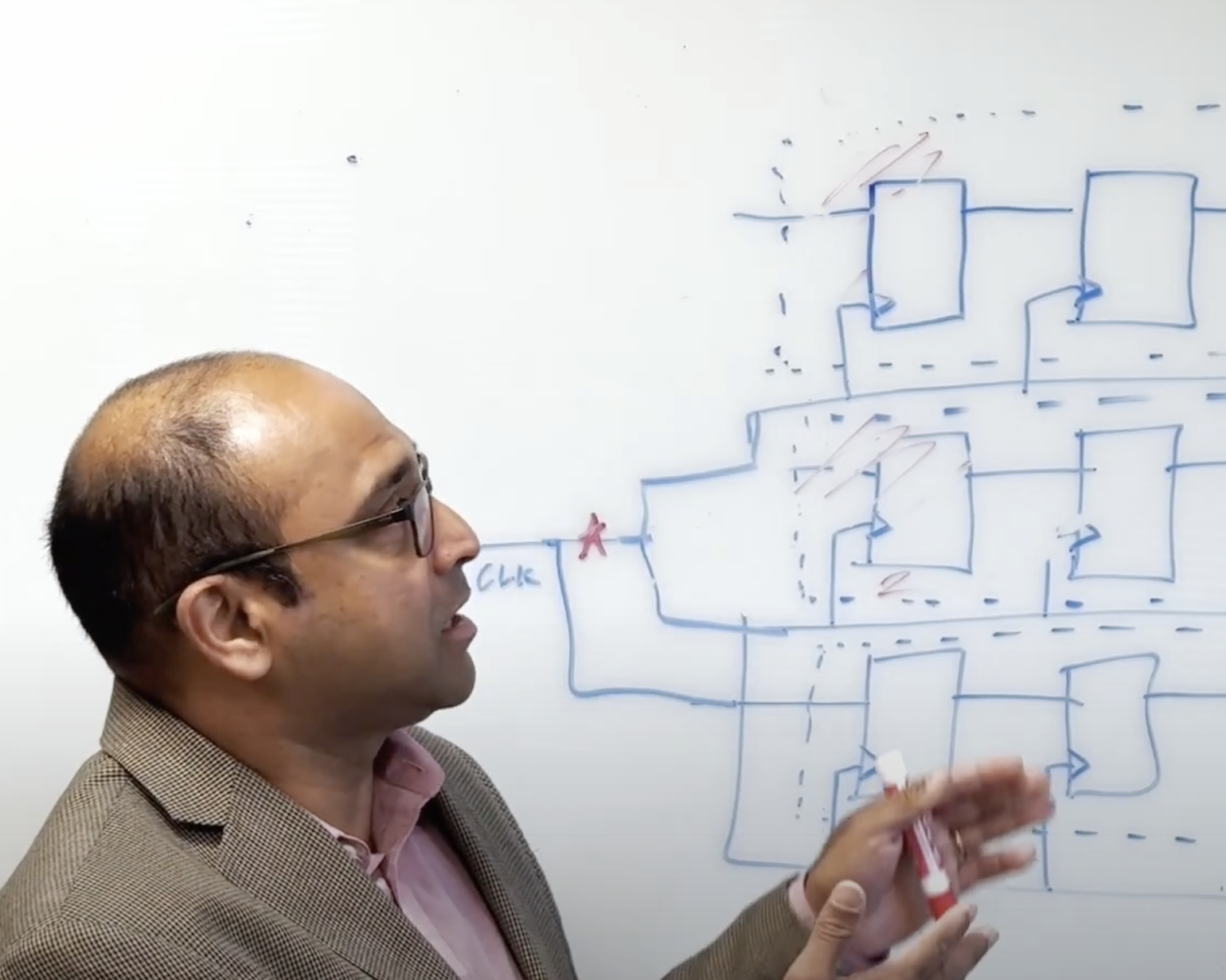

An explosion in design complexity is significantly impacting traditional testing approaches in the semiconductor sector. As transistor density increases and chip architectures evolve, conventional methods are becoming inadequate to handle the challenges posed by these advancements. Jayant D’Souza, the technical product director for yield learning products at Siemens EDA’s Tessent group, emphasizes that these shifts are crucial in understanding the testing landscape.

One major challenge includes the emergence of defects within clock trees that power scan chains, as well as within blocks of scan cells which can contain millions of components. This complexity increases the potential for errors during the chip manufacturing process, requiring more sophisticated testing strategies.

The industry is also witnessing a move toward backside power delivery, which introduces additional layers of complexity in chip design and testing. As devices continue to scale, the demand for more accurate testing processes is becoming more critical. Consequently, engineers and manufacturers must adapt their testing methods to accommodate these ongoing changes.

To effectively navigate these challenges, D’Souza advocates for the integration of machine learning into the testing framework. By utilizing machine learning algorithms, companies can develop Pareto charts to categorize various types of defects more efficiently. This approach allows for targeted testing efforts, which enhance the ability to identify and address defect sources promptly.

Overall, the shift in design complexity and architecture, coupled with the potential of machine learning, presents a transformative opportunity for improving testing processes in semiconductor manufacturing. As the sector continues to evolve, it is imperative for companies to embrace these innovations to maintain product quality and reliability.

The content above is a summary. For more details, see the source article.